'CERASITE' - DIPスケールFPGAボード

Overview

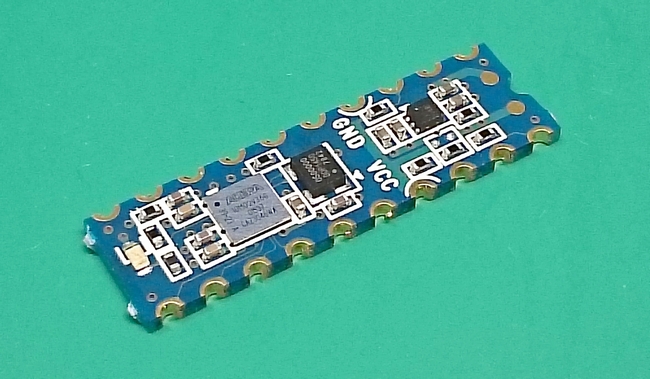

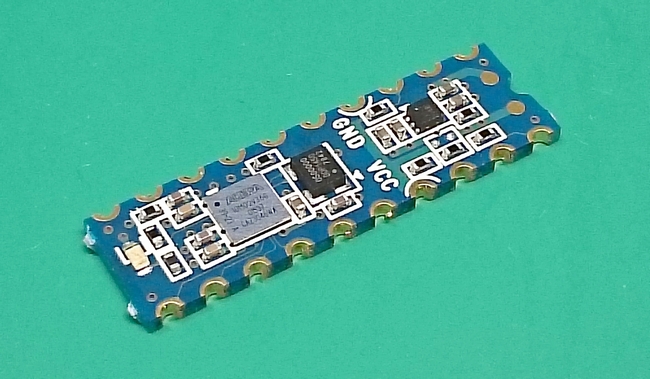

CERASITE(セラサイト) C-02は300mil幅DIPサイズの超小型のFPGAボードです。

Altera MAX10 FPGA搭載し、電源回路、OSCをコンパクトに集積しています。外形寸法は300mil幅20ピンDIP ICと同等になっており、ユニバーサル基板やブレッドボードでのプロトタイピングに最適です。

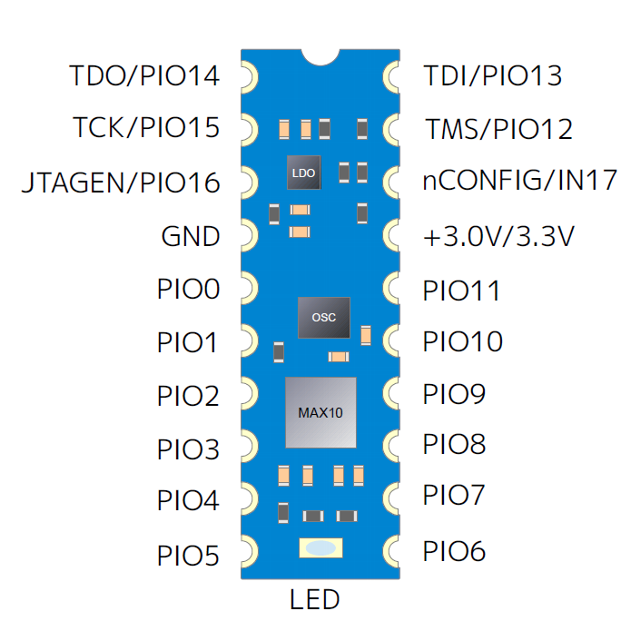

- 300mil幅20ピンDIPサイズ (25.7 mm × 7.6 mm)

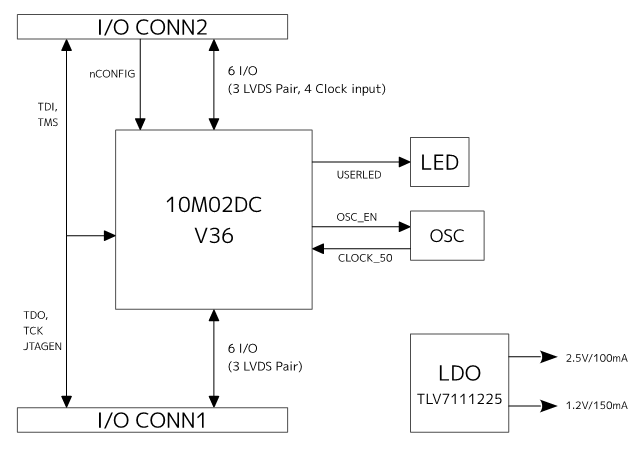

- Altera MAX10 10M02DCV36 (2kLEs, 108kbitメモリー, 96kbit flash, VBGA36)

- オンボードOSC (50.0 MHz)

- 最大17本のユーザーI/O数

- 3.0V/3.3V単電源駆動

- ユーザーLEDを1個搭載

- PCBに直接マウント可能な片面実装

- ユニバーサル基板で使いやすい端面スルーホール

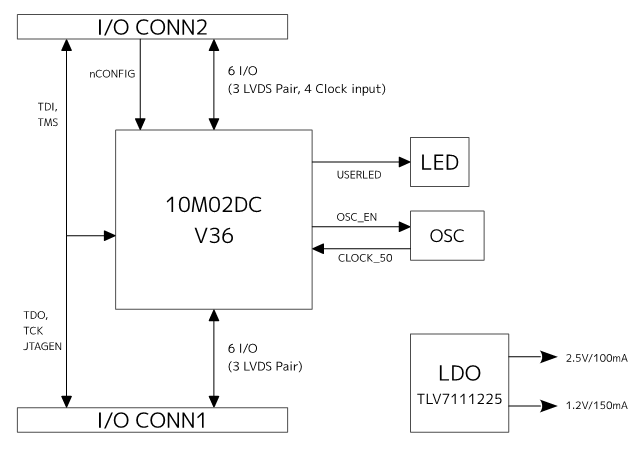

C-02 ボードブロック図

使用許諾

ご使用の前に、本モジュールについて下記事項を了承の上で使用してください。

- 直射日光に晒される場所、高温や低温になる場所、結露・氷結の発生する場所、過度の衝撃や振動の発生する場所で使用しないでください。また高信頼性が必要な箇所には使用できません。

- 本モジュール上のパッケージは大変割れやすくなっています。モジュールを曲げたり衝撃を与えたりすると破損する恐れがあります。取り扱いには十分注意してください。

- 本モジュールは試作およびホビー用として設計されています。一般製品を意図した逆接続、逆挿入、過電圧等の保護はされていません。誤った使用は破損、発煙、発火の原因となります。

- 本モジュールを使用して発生した直接的、間接的損害について開発元および販売元は一切の責務を負いません。

- 本モジュールの内容および使用、測定データ、技術情報、サポート等に関してのお問い合わせは原則としてお答えできません。

- 部品調達や性能改善に伴い、予告なく仕様または部品の変更を行う場合があります。

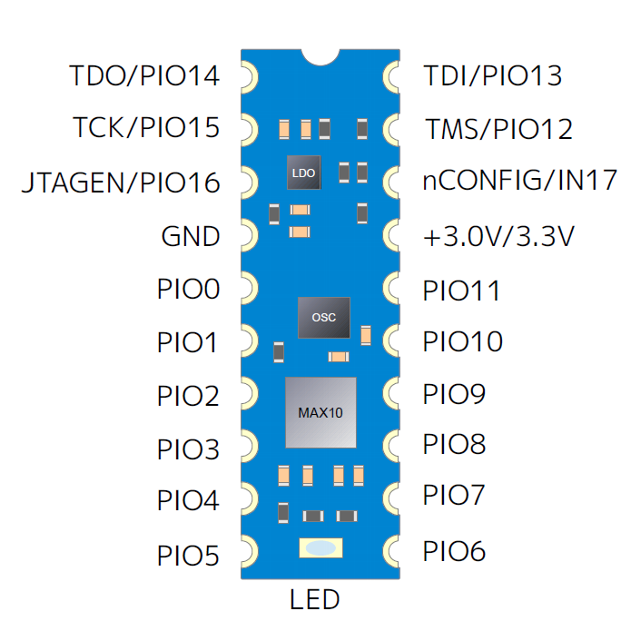

ボードピン配置図

- TDO, TCK, TDI, TMSおよびJTAGENはユーザーI/Oと排他利用です。

- nCONFIGは入力専用ピンです。

- デバイスやI/O機能の詳細はIntel MAX10デバイスデータシートを参照してください。

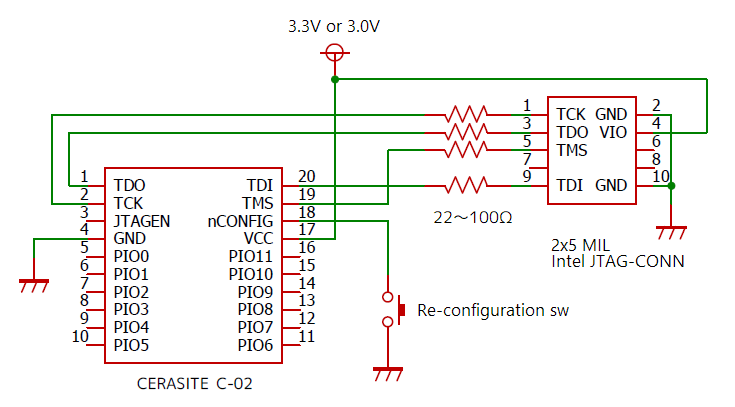

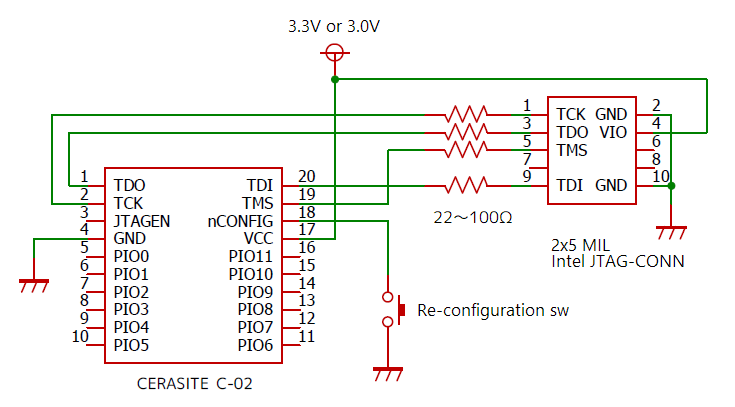

代表的な結線

- 3, 18, 19, 20番ピンは内部で10kΩでプルアップされています。また2番ピンは内部で1kΩでプルダウンされています。

- nCONFIGピンをユーザーI/Oとして使う場合は入力ピンとしてのみ使用できます。

- JTAGピンをユーザーI/Oとして使う場合はJTAGENピンは機能切り替えピンとして動作し、ユーザーI/Oとしては使えません。ユーザーI/Oに切り替える場合はJTAGENピンは1kΩでプルダウンします。JTAG機能に切り替える場合はJTAGENピンをHレベルに固定します。

- ⚠️ QuartusPrime 21.1以降 において書き込み・ベリファイ・ブランクチェック不良の発生が確認されています。20.1以前のバージョンをご利用下さい。

ダウンロード

C-02 取り扱い説明書 (PDF)

c-02_manual_v1.1.pdf

c-02_manual_v1.1.pdf

C-02 回路図 (PDF)

cerasite_c-02_schm.pdf

cerasite_c-02_schm.pdf

購入先

CERASITE - DIPスケールFPGAボード

CERASITE - DIPスケールFPGAボード

Mail - support@j7system.jp (初期不良等につきましては購入先にお問い合わせください)

GitHub - osafune

©2014-2024 S.OSAFUNE, J-7SYSTEM WORKS LIMITED.

c-02_manual_v1.1.pdf

cerasite_c-02_schm.pdf